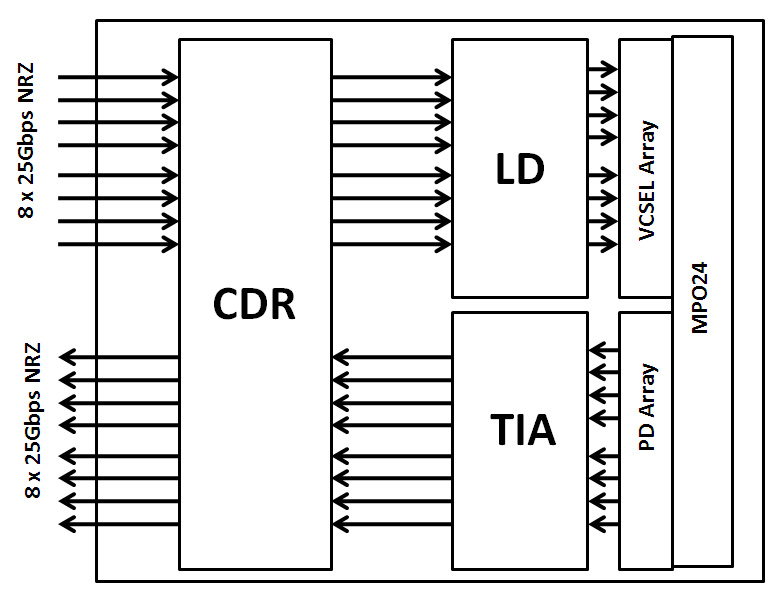

2x100GBASE-SR4 O transceptor QSFPDD é um tipo de transceptor paralelo, o pacote VCSEL e PIN array é a técnica chave, através do sistema I2C pode entrar em contato com o módulo. É uma densidade dupla QSFP de oito canais, plugável, paralela, fibra óptica para aplicações Ethernet de 2x100 Gigabit, módulo de alto desempenho para aplicações de interconexão e comunicação de dados multi-pista de curto alcance. Ele integra oito faixas de dados em cada direção com largura de banda de 8x25.78125Gbps. Cada pista pode operar a 25,78125 Gbps até 70 m usando fibra OM3 ou 100 m usando fibra OM4. Esses módulos são projetados para operar em sistemas de fibra multimodo usando um comprimento de onda nominal de 850nm. A interface elétrica usa um conector do tipo borda de contato 76. A interface óptica usa um conector MTP (MPO) de 24 fibras. Este módulo incorpora circuito comprovado e tecnologia VCSEL para fornecer longa vida confiável, alto desempenho e serviço consistente.

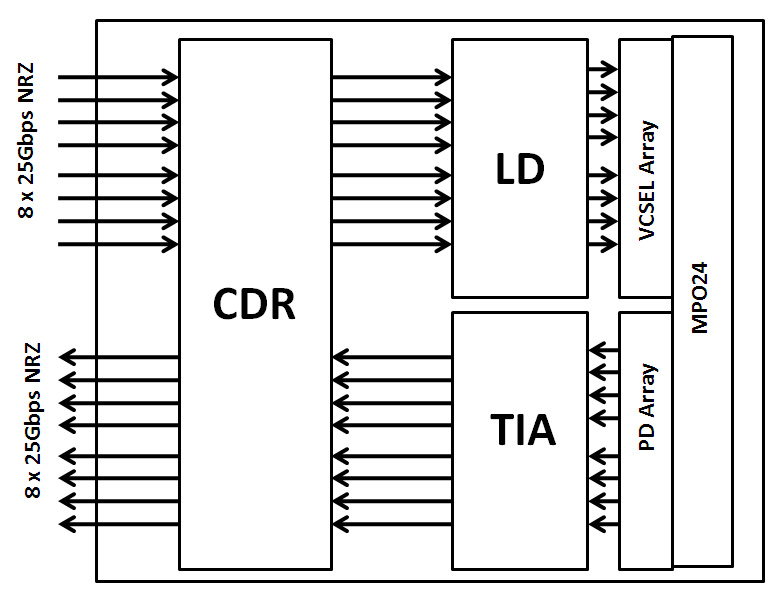

Figura 1. Módulo diagrama de bloco

Características

● 8 canais full-duplex módulos transceptor

● Taxa de transmissão de dados até 26Gbps por canal

● 8 canais 850nm VCSEL matriz

● 8 canais PIN matriz detector de fotos

● Circuitos CDR internos em ambos os canais do receptor e do transmissor

● Suporte CDR bypass

● Baixo consumo de energia <4W

● Fator de forma QSFP DD Pluggable quente

● Comprimento máximo do link de 70m em fibra multimodo OM3 (MMF) e 100m em OM4 MMF

● Receptáculo do conector MPO24

● Temperatura do caso de operação 0 °C a 70 °C

● Tensão de alimentação 3.3V

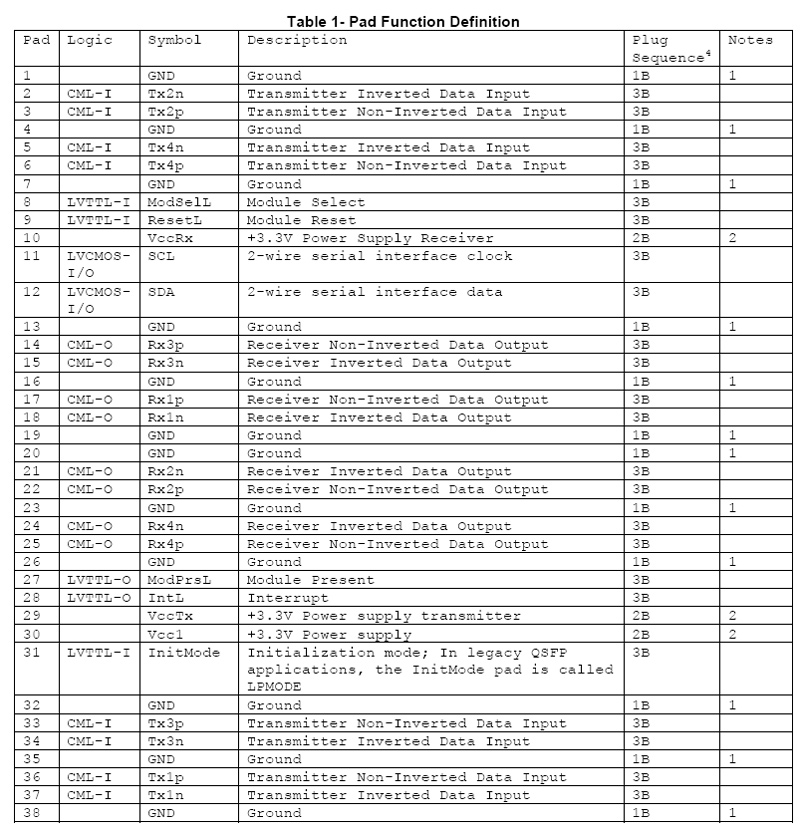

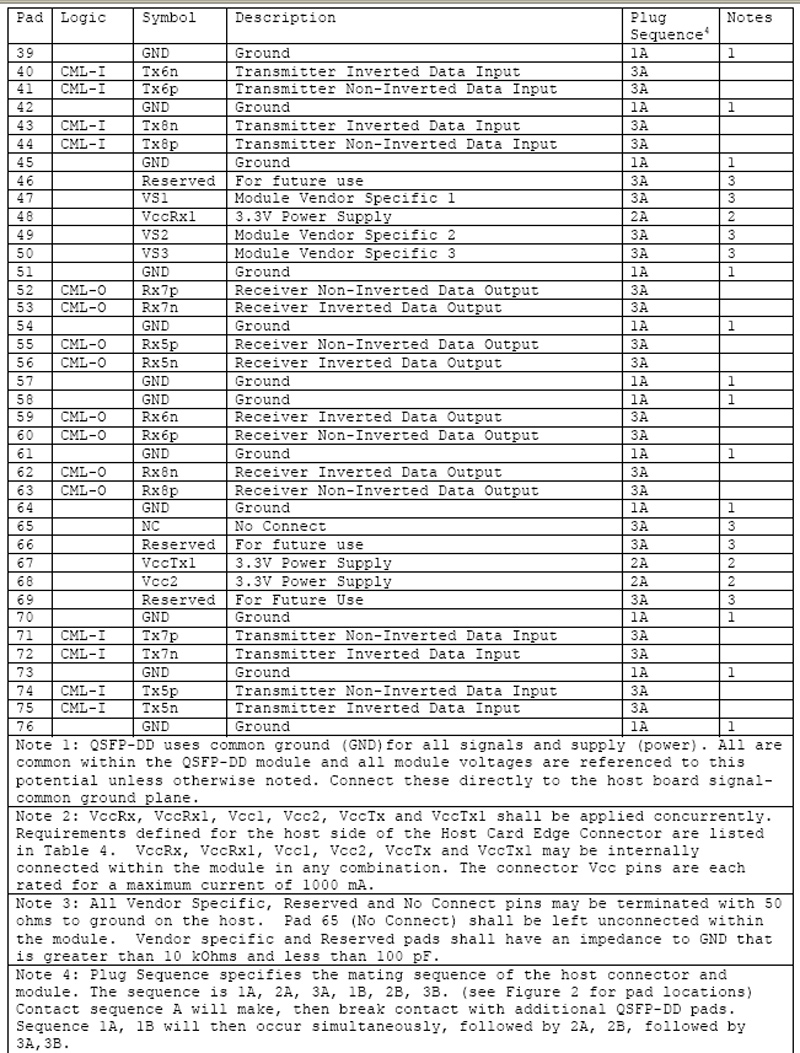

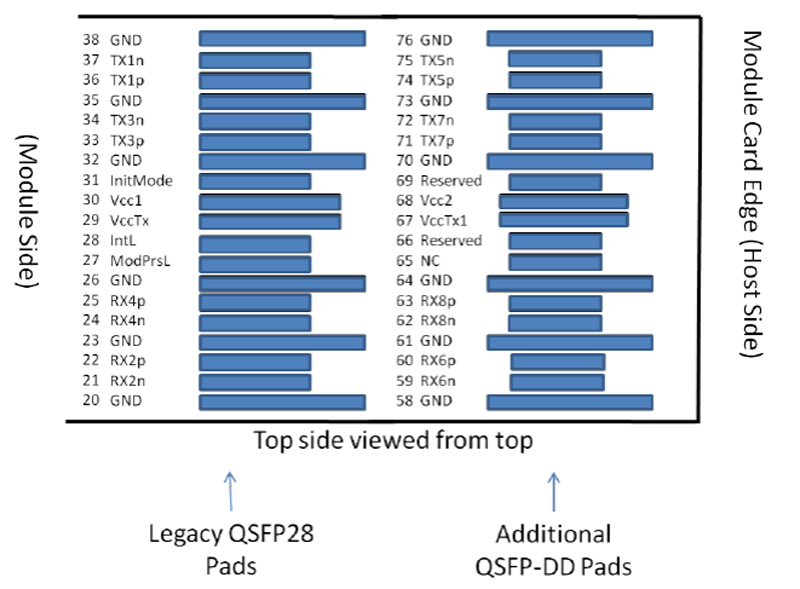

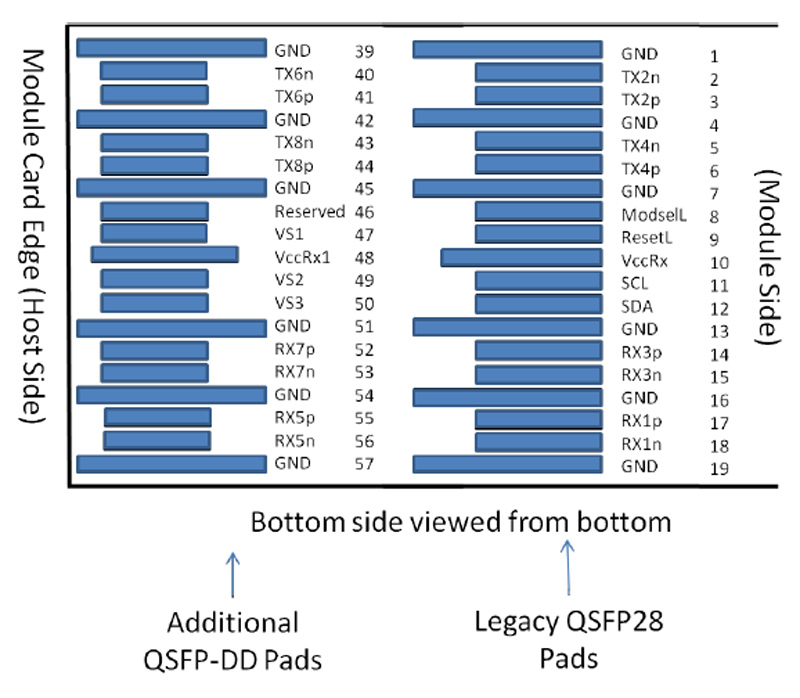

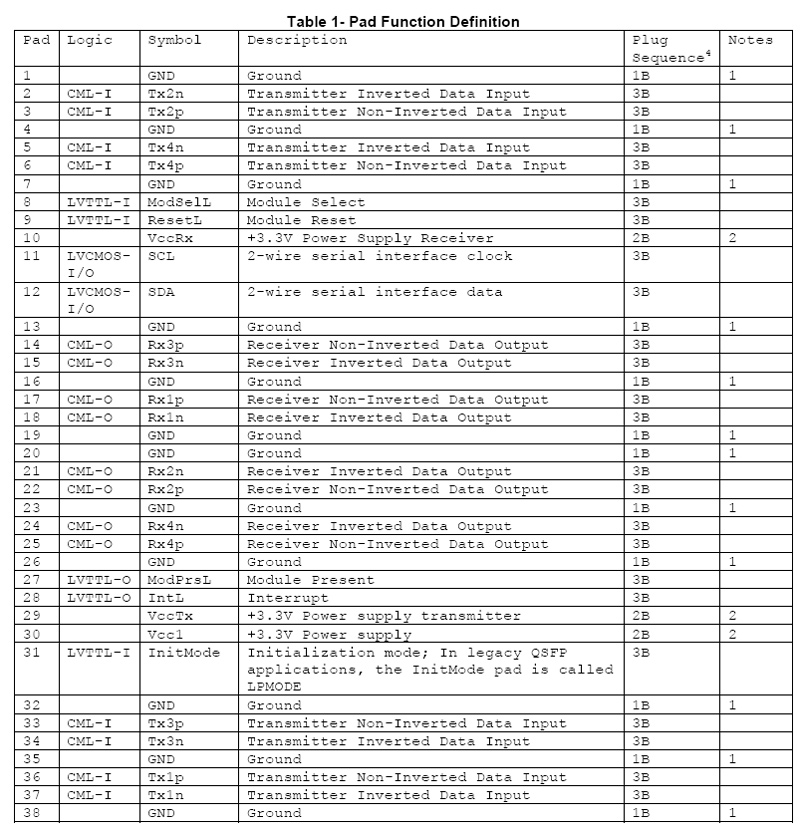

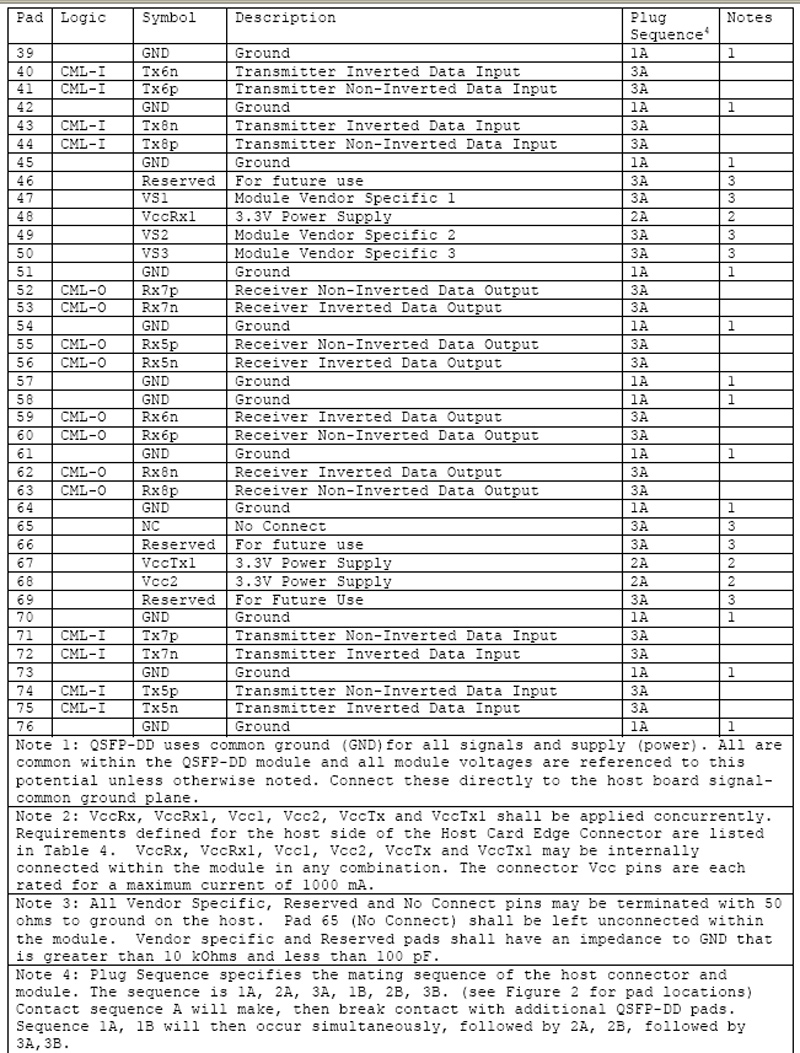

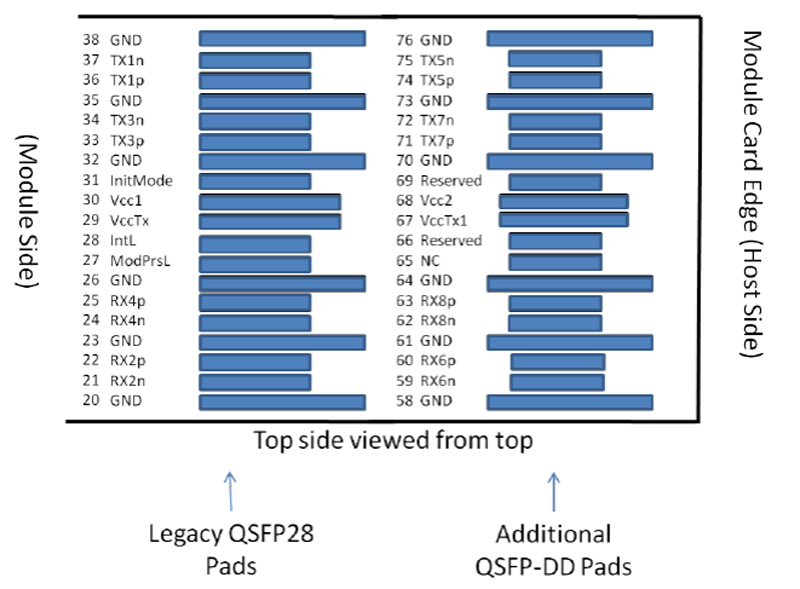

Pin Deion

Figura 2. Detalhes elétricos Pin-out

Pino ModSelL

O ModSelL é um sinal de entrada que deve ser puxado para Vcc no módulo QSFP-DD. Quando mantido baixo pelo host, o módulo responde a comandos de comunicação serial de 2 fios. O ModSelL permite o uso de vários módulos de QSFP-DD em um único barramento de interface de 2 fios. Quando ModSelL é “Alto”, o módulo não deve responder ou reconhecer qualquer comunicação de interface de 2 fios do host.

A fim de evitar conflitos, o sistema host não deve tentar comunicações de interface de 2 fios dentro do tempo de desafirmação ModSelL após a escritura de quaisquer módulos de QSFP-DD. Da mesma forma, o host deve esperar pelo menos pelo período do tempo de afirmação ModSelL antes de se comunicar com o módulo recém-criado. Os períodos de afirmação e desafirmação de diferentes módulos podem se sobrepor desde que os requisitos de tempo acima sejam atendidos.

Pino ResetL

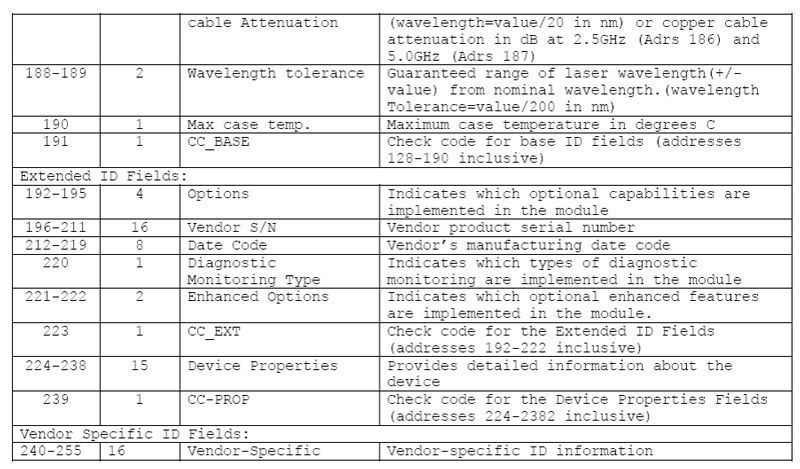

O sinal ResetL deve ser puxado para Vcc no módulo. Um nível baixo no sinal ResetL por mais tempo do que o comprimento de pulso mínimo (t_Reset_init) (consulte a Tabela 13) inicia uma redefinição completa do módulo, retornando todas as configurações do módulo do usuário ao seu estado padrão.

Pin InitMode

InitMode é um sinal de entrada. O sinal InitMode deve ser puxado até Vcc no módulo QSFP-DD. O sinal InitMode permite que o host defina se o módulo de QSFP-DD será inicializado sob controle de software host (InitMode afirmado High) ou controle de hardware de módulo (InitMode deasserted Low). Sob o controle de software host, o módulo deve permanecer no modo de baixa potência até que o software permita a transição para o modo de alta potência, conforme definido na seção 7.5. Sob controle de hardware (InitMode desafirmado Low), o módulo pode imediatamente fazer a transição para o Modo de Alta Potência após a interface de gerenciamento ser inicializada. O host não deve alterar o estado deste sinal enquanto o módulo estiver presente. Em aplicativos QSFP legados, este sinal é denominado LPMode. Veja SFF-8679 para o sinal deion.

Pino ModPrsL

ModPrsL deve ser puxado até Vcc Host na placa host e aterrado no módulo. O ModPrsL é declarado “Baixo” quando o módulo é ed e desafirmado “Alto” quando o módulo está fisicamente ausente do conector host.

Pino IntL

IntL é um sinal de saída. O sinal IntL é uma saída de coletor aberto e deve ser puxado para Vcc Host na placa de host. Quando o sinal IntL é declarado Baixo, ele indica uma mudança no estado do módulo, uma possível falha operacional do módulo ou um status crítico para o sistema host. O host identifica a origem da interrupção usando a interface serial de 2 fios. O sinal IntL é desafirmado “Alto” depois que todos os sinalizadores de interrupção definidos são lidos.

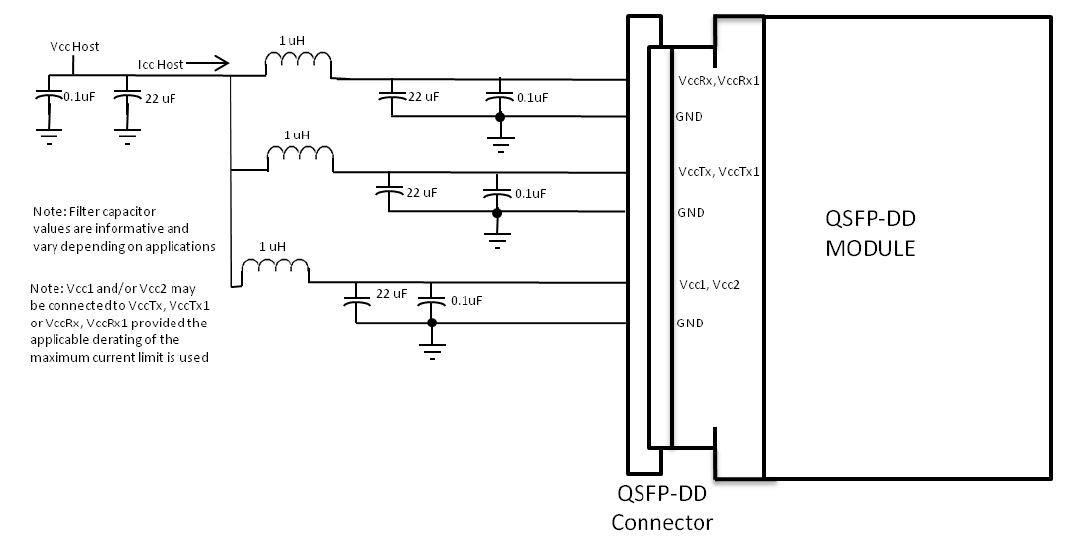

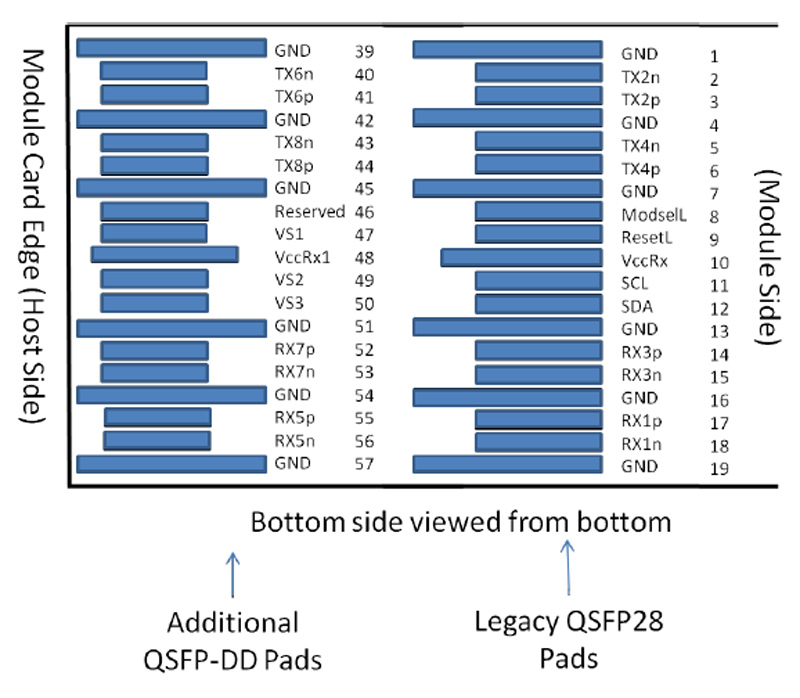

Filtragem da fonte de alimentação

A placa do anfitrião deve usar a filtragem da fonte de alimentação mostrada na Figura3.

Figura 3. Filtragem da fonte de alimentação da placa do anfitrião

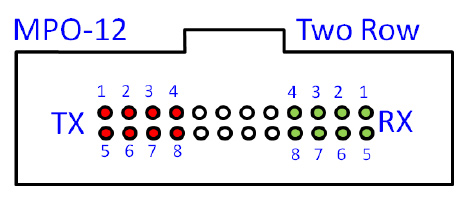

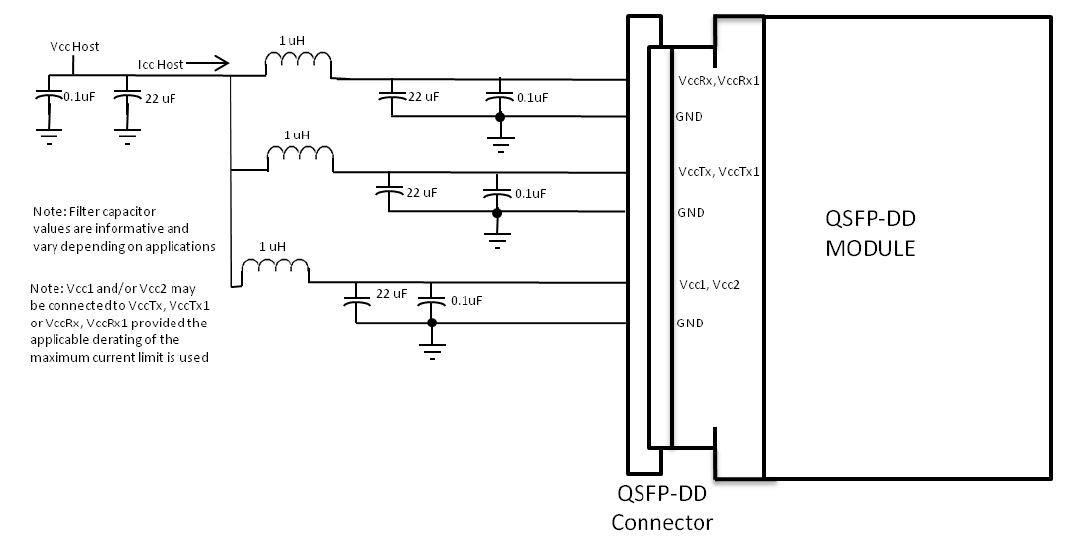

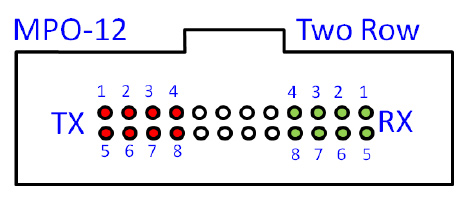

Faixas de interface óptica e atribuição

A porta de interface óptica é um conector MPO24 macho.

Figura 4. receptáculo óptico e orientação do canal

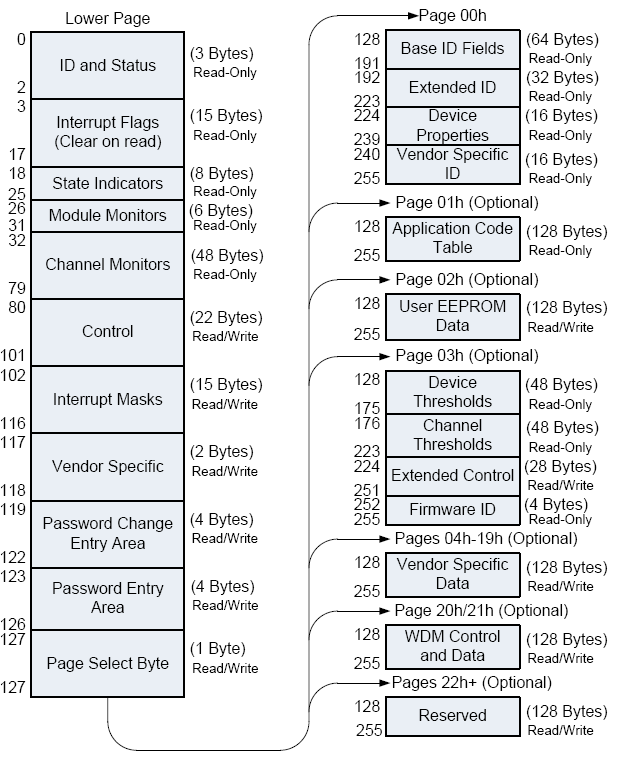

INTERFACE DE MONITORAMENTO DIAGNÓSTICO (OPCIONAL)

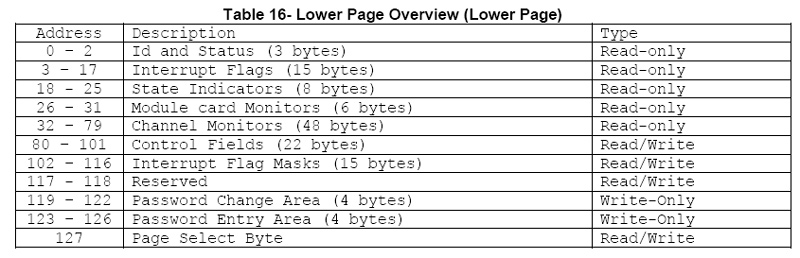

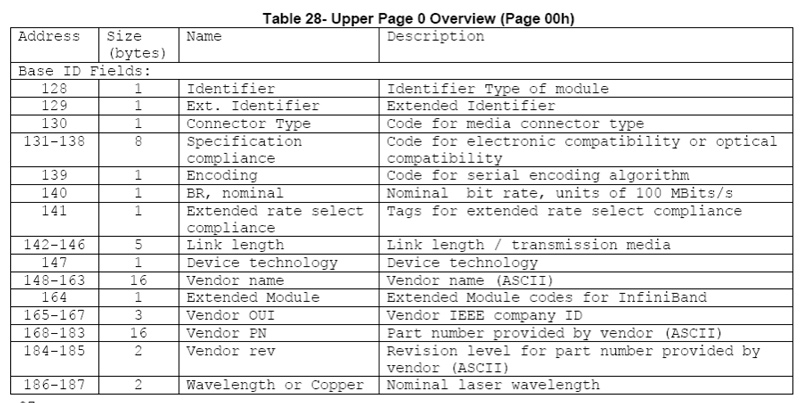

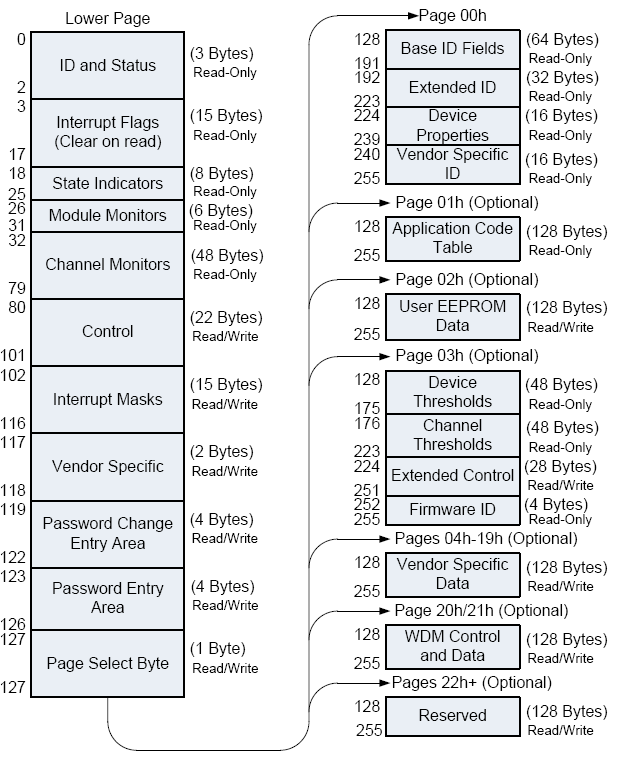

A função de monitoramento de diagnósticos digitais está disponível em todos os produtos QSFP DD. Uma interface serial de 2 fios fornece ao usuário o contato com o módulo. A estrutura da memória é mostrada na Figura 5. o espaço de memória é organizado em uma página única, inferior, espaço de endereço de 128 bytes e múltiplas páginas de espaço de endereço superior. Essa estrutura permite acesso oportuno a endereços na página inferior, por exemplo, Interromper Bandeiras e Monitores. Menos entradas críticas de tempo, por exemplo, informações de ID serial e configurações de limite, estão disponíveis com a função Selecionar página. A estrutura também fornece expansão de endereço adicionando páginas superiores adicionais conforme necessário. O endereço de interface usado é A0xh e é usado principalmente para dados críticos de tempo, como manipulação de interrupção, a fim de permitir uma leitura única para todos os dados relacionados a uma situação de interrupção. Após uma interrupção, IntL, foi afirmada, o host pode ler o campo de bandeira para determinar o canal afetado e o tipo de bandeira.

Figura 5. Mapa de memória QSFP DD

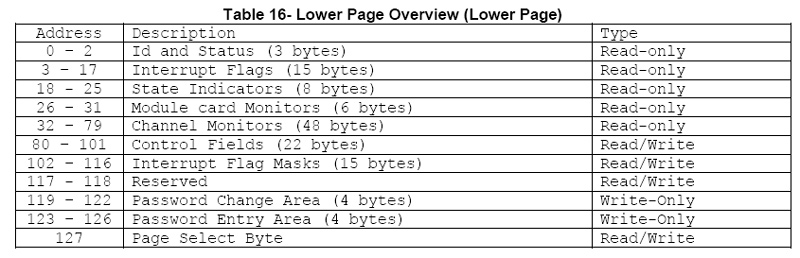

Figura 6. Mapa de memória baixa

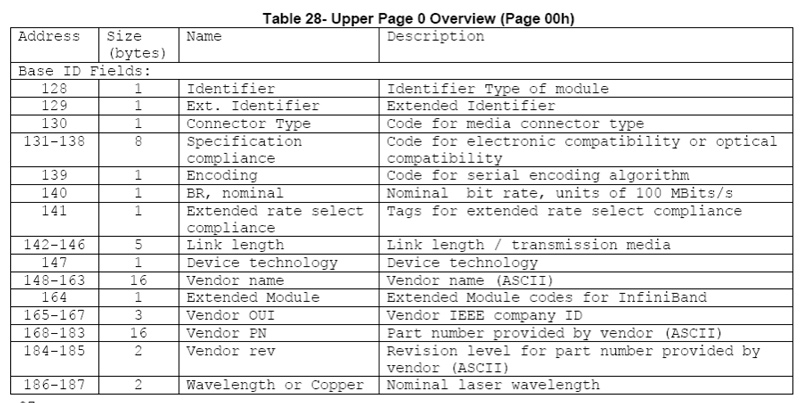

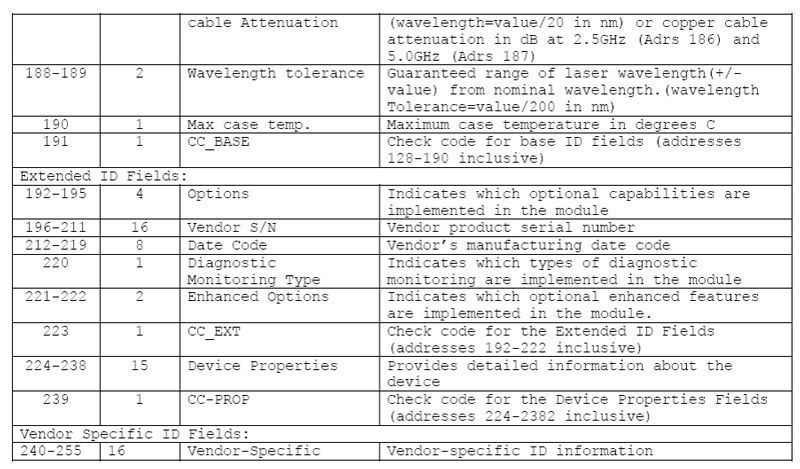

Figura 7. Página 00 Mapa de Memória

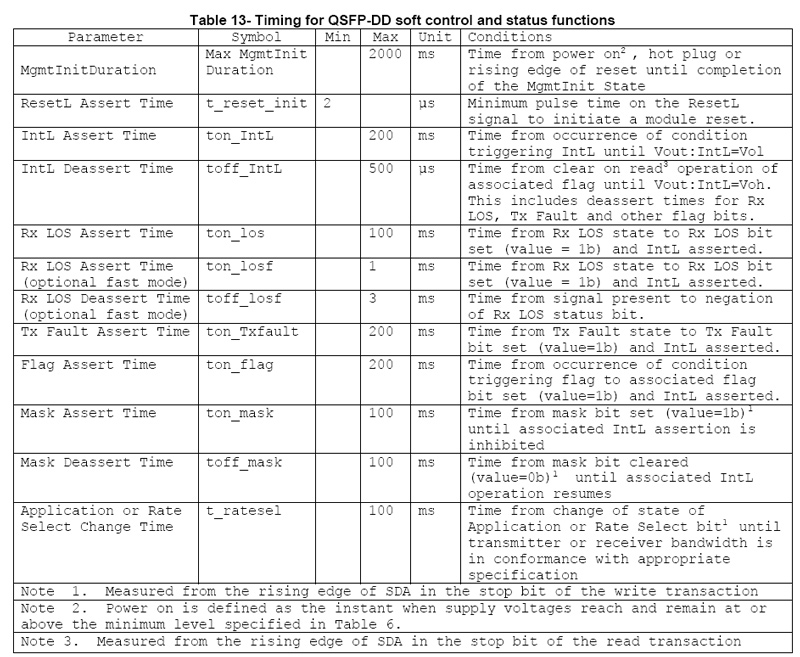

Temporização para funções de controle suave e status

Figura 9. Especificações de temporização

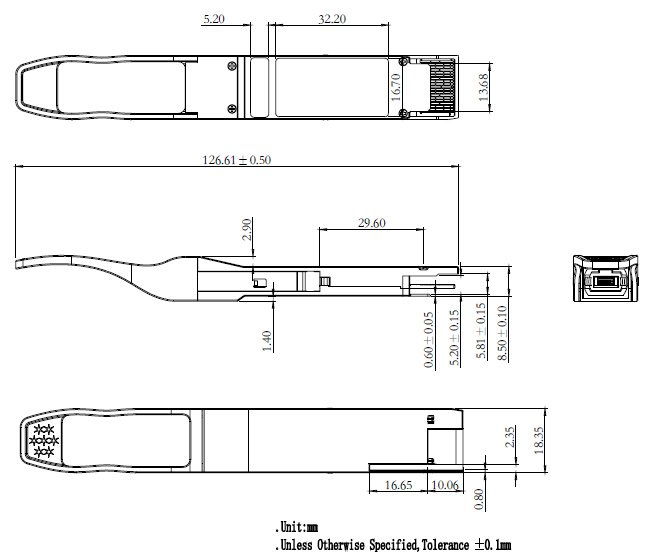

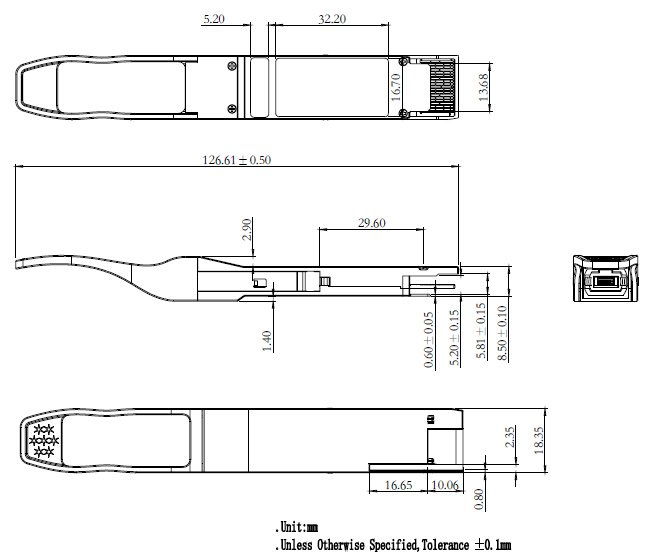

Desenho de contorno (mm)

Avaliações máximas absolutas

Parâmetro | Símbolo | Min | Max | Unidade |

Tensão de alimentação | Vcc | -0,3 | 3.6 | V |

Tensão de entrada | Vin | -0,3 | Vcc + 0,3 | V |

Temperatura de armazenamento | Tst | -20 | 85 | °C |

Temperatura de funcionamento do caso | Top | 0 | 70 | °C |

Umidade (não-condensando) | Rh | 5 | 95 | % |

Condições operacionais recomendadas

Parâmetro | Símbolo | Min | Típico | Max | Unidade |

Fornecimento Tensão | Vcc | 3.13 | 3.3 | 3,47 | V |

Operando Capa Temperatura | Tca | 0 |

| 70 | °C |

Taxa de dados Per Lane | Fd |

| 25.78125 |

| Gbps |

Umidade | Rh | 5 |

| 85 | % |

Dissipação de energia | Pm |

|

| 4 | W |

Especificações elétricas

Parâmetro | Símbolo | Min | Típico | Max | Unidade |

Diferencial Entrada Impedância | Zin | 90 | 100 | 110 | Ohm |

Diferencial Saída Impedância | Zout | 90 | 100 | 110 | Ohm |

Diferencial Tensão de entrada Amplitude AAmplitude | ΔVin | 300 |

| 1100 | MVp-p |

Saída diferencial Amplitude de tensão | ΔVout | 500 |

| 800 | MVp-p |

Desvio | Sw |

|

| 300 | Ps |

Taxa de erro de bits | BER |

|

| 5E-5 |

|

Lógica de entrada Nível alto | VIH | 2.0 |

| VCC | V |

Lógica de entrada Nível baixo | VIL | 0 |

| 0,8 | V |

Lógica de saída Nível alto | VOH | VCC-0.5 |

| VCC | V |

Lógica de saída Nível baixo | VOL | 0 |

| 0,4 | V |

Nota:

1. BER = 5E-5; PRBS 2 ^ 31-1@25.78125Gbps. Pré-FEC

2. A amplitude da tensão de entrada diferencial é medida entre TxnP e TxnN.

3. A amplitude da tensão de saída diferencial é medida entre RxnP e RxnN.

Características ópticas

Tabela 3-Características ópticas

Parâmetro | Símbolo | Min | Típico | Max | Unidade | Notas |

Transmissor |

Comprimento de onda do centro | Λc | 840 | 850 | 860 | Nm | - |

Largura espectral RMS | ∆Λ | - | - | 0,6 | Nm | - |

Potência média de lançamento, Cada pista | Pia | -8,4 | - | 2.4 | DBm | - |

Modulação óptica Amplitude (OMA), cada faixa | OMA | -6,4 |

| 3 | DBm | - |

Transmissor e Olho de dispersão Fechamento (TDEC), cada pista | TDEC |

|

| 4.3 | DB |

|

Relação de extinção | ER | 3 | - | - | DB | - |

Lançamento médio Poder de OFF Transmissor, Cada pista |

|

|

| -30 | DB | - |

Máscara de olho Coordenadas: X1, X2, X3, Y1, Y2, Y3 | VALORES DE ESPECIFICAÇÃO {0,3, 0,38, 0,45, 0,35, 0,41,0,5} | Relação de acerto = 5x10-5

|

Receptor |

Comprimento de onda do centro | Λc | 840 | 850 | 860 | Nm | - |

Receptor estressado Sensibilidade em OMA |

|

|

| -5.2 | DBm | 1 |

Média máxima Poder no receptor, Cada pista Entrada, cada pista |

|

|

| 2.4 | DBm | - |

Média mínima Poder no receptor, Cada pista

|

|

|

| -10,3 | DBm |

|

Reflectância do receptor |

|

|

| -12 | DB | - |

LOS Assert |

| -30 |

|

| DBm | - |

LOS De-Assert - OMA |

|

|

| -7,5 | DBm | - |

Histerese de LOS |

| 0,5 |

|

| DB | - |

Nota:

1. Medido com sinal de teste de conformidade em TP3 para BER = 5E-5 por-FEC

Aplicações

● IEEE 802.3bm 100GBASE SR4

Centro de dados da Internet

Centro de dados da Internet Perguntas frequentes

Perguntas frequentes Notícias da Indústria

Notícias da Indústria Sobre nós

Sobre nós Interruptor do centro de dados

Interruptor do centro de dados  Interruptor da empresa

Interruptor da empresa  Interruptor industrial

Interruptor industrial  Interruptor de acesso

Interruptor de acesso  Rede integrada

Rede integrada  Módulo óptico & Cabo

Módulo óptico & Cabo

Ligue para nós:

Ligue para nós:  Envie-nos um e-mail:

Envie-nos um e-mail:  2106B, # 3D, Cloud Park Fase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Fase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.