Os módulos DCO QSFP-DD 400G ZR são baseados em DP- 16QAM suportando banda C estendida, detecção coerente de diversidade de polarização e equalização de link eletrônico avançado. A compensação de dispersão cromática pode ser aplicada ao lado receptor do demodulador. Este módulo é gerenciado utilizando a Interface de Dois Fios que é especificada na Common Management Interface Specification (CMIS).

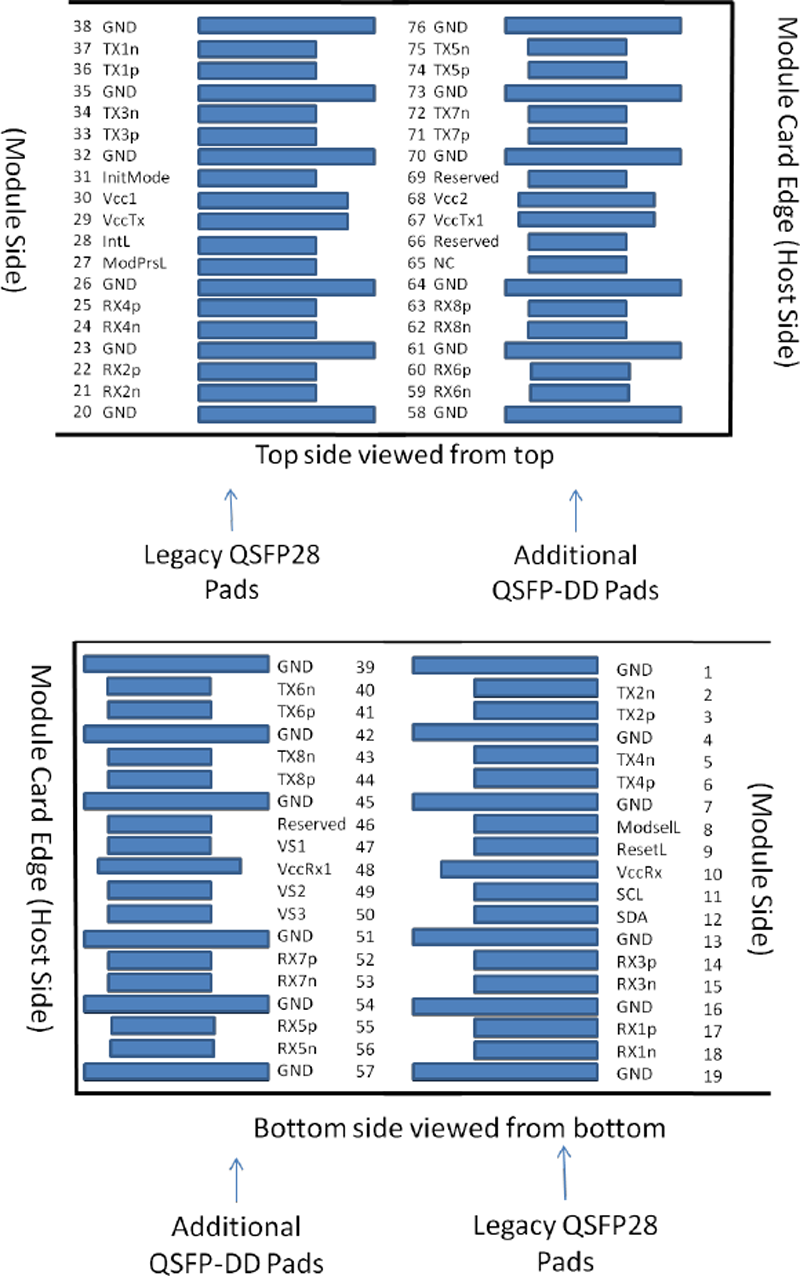

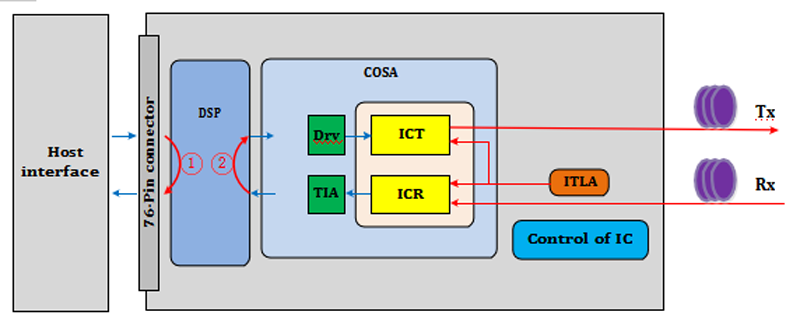

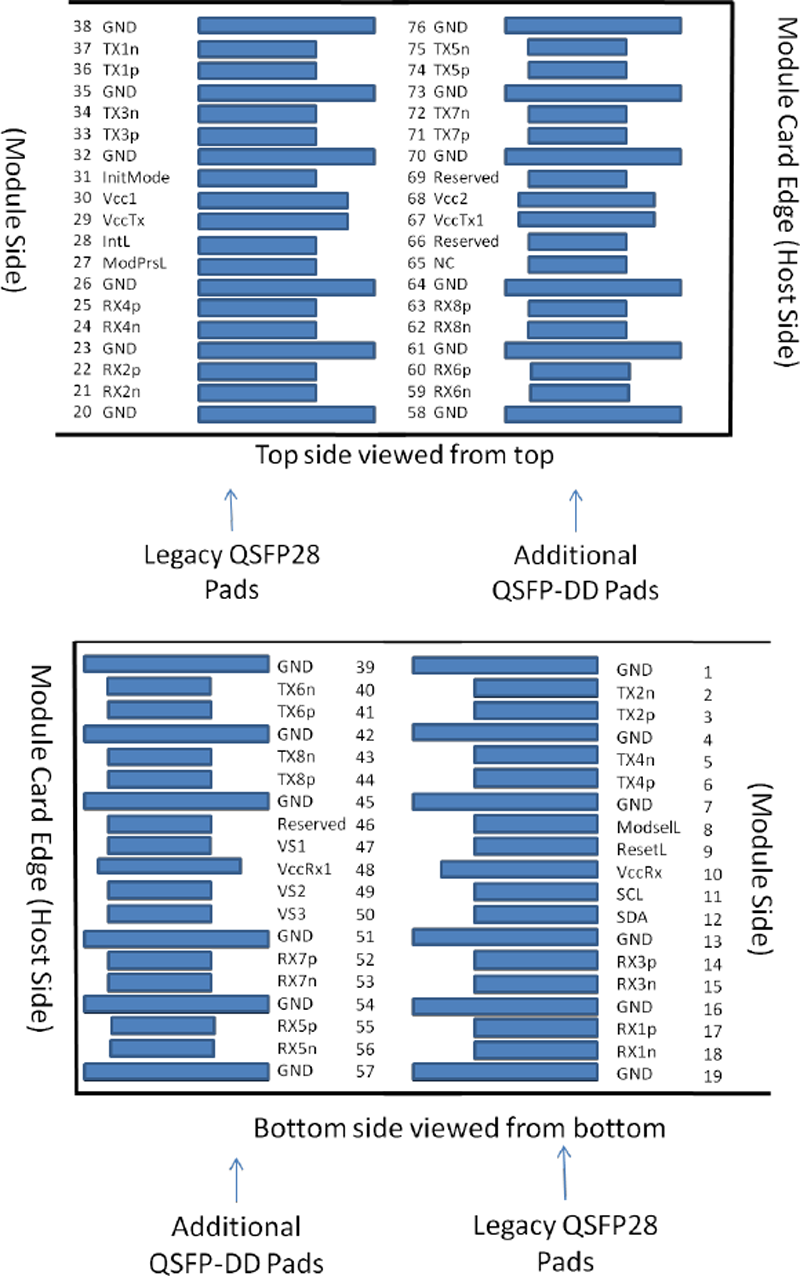

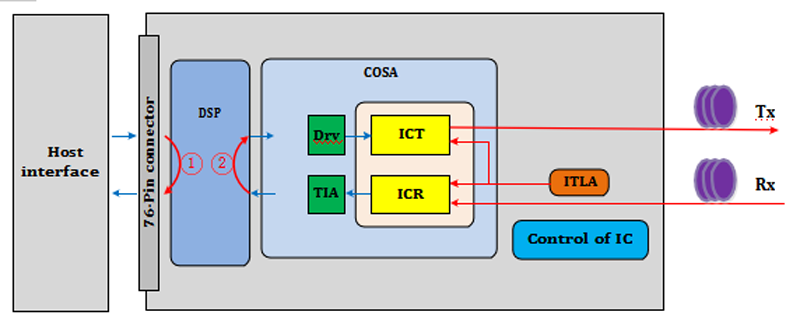

O módulo usa um conector de especificação de hardware QSFP-DD MSA QSFP-DD de 76 pinos para todas as interfaces elétricas com a placa host, enquanto as interfaces ópticas no lado da linha são fornecidas através dos receptáculos ópticos no QSFP-DD. O módulo pode ser dividido em três partes funcionais: caminho TX, caminho RX e bloco de controle e energia.

A interface host é composta por um total de 8 pistas SerDes de alta velocidade. Isso permite que o módulo suporte uma interface para uma aplicação de 400G: uma interface de cliente de modo duplo independente de 4 pistas (para aplicação de 400GbE) e quatro interfaces de cliente de modo de pista dupla independentes (para aplicação 4 * 100GbE).

A interface de comunicação de gerenciamento fornece uma série de operações de gerenciamento elementares que permitem ao host ler ou gravar em registros de gerenciamento de tamanho de byte no mapa de memória de gerenciamento do módulo. Existem operações de leitura e gravação para bytes únicos e para sequências de bytes contíguas. Dois tipos de operações de leitura, com endereçamento implícito (lido no endereço atual) ou com endereçamento explícito, são suportados.

A interface de comunicação de gerenciamento distingue uma função e uma função. O host deve ser o e o módulo deve ser o s.

O inicia todas as operações que levam à transferência de dados. Os dados podem ser transferidos do para o s (em operações de gravação) e do s para o (em operações de leitura).

Características

● Suporte para espaçamento de canal Flex-grid DWDM em banda C

● Suporte Interfaces do lado do cliente: 400GAUI-8/4*100GAUI-2

● Suporte de DP-16QAM do lado da linha com CFEC

● Fator de forma padrão tipo 2 de QSFP-DD

● Conector compatível com MSA QSFP-DD 76pin

● Compatível com CMIS 5.0

● Em conformidade com o Acordo de Implementação da OIF para CMIS Coerente, Rev 01.1

● OIF-400ZR-01.0_reduced2.pdf

● Compatível com RoHS

Aplicação típica

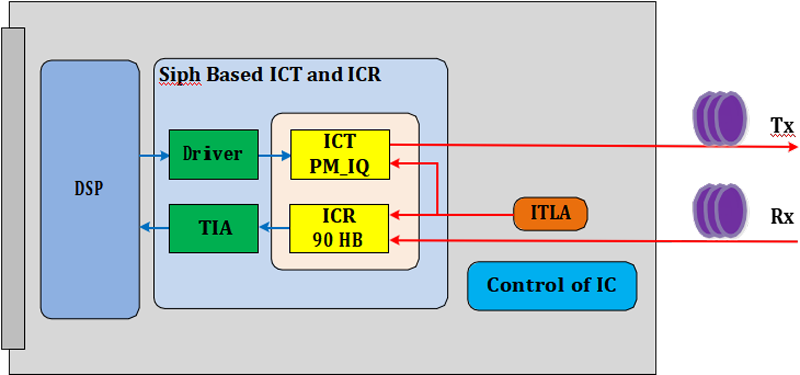

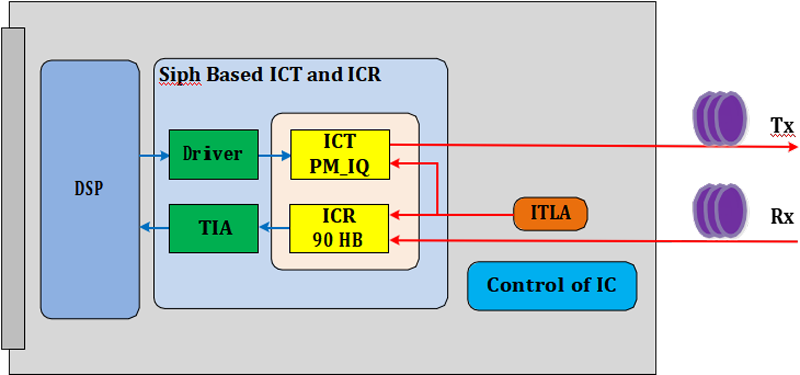

O campo de aplicação do módulo é amplamente utilizado de interconexões de curta distância (ZR) a Metro(MR). Como mostrado na figura 1, é composto de faixas de alta dados, uma única fonte de alimentação de 3,3 V, uma interface IIC para controle de módulo e relatório de status, e pinos de alarme e controle dedicados (não mostrados na figura 1).

Figura 1. Diagrama do bloco do transceptor

Interface de Anfitrião

O suporte do módulo para aplicações amplas com interfaces Host: 400GAUI-8/100GUI-2. A interface Host está em conformidade com os padrões de protocolo existentes e opera com as especificações de camada física padrão. A terminação, mapeamento e/ou agregação deste sinal está em uma estrutura de quadro ZR interna. A estrutura de quadro ZR é então adaptada para o motor CFEC e DSP enquadrado para transmissão sobre a interface de mídia coerente. A sinalização da interface Host está em conformidade com o protocolo existente e os padrões elétricos, conforme definido pelo IEEE 802.3TM-2018.

A Interface Host compatível com interface elétrica de chip para módulo de alta velocidade de alcance muito curto CEI-56G VSR-PAM4 para codificação PAM4.

Interface de Anfitrião | Taxa de dados de aplicação | Contagem de pista | Taxa de sinalização de pista | Modulação |

400GAUI-8 | 425,00 Gb/s | 8 | 26,5625 GBaud ( /- 100 ppm) | PAM4 |

4*100GAUI-8 | 4*106,25 Gb/s | 8 | 26,5625 GBaud ( /- 100 ppm) | PAM4 |

Interface de mídia

A interface de mídia utiliza modulação DP-16QAM, detecção coerente de diversidade de polarização e equalização de link eletrônico avançado com dispersão somática e compensação de atraso de grupo diferencial.

O módulo termina o sinal da interface do host, em seguida, mapeia e agrega-os em uma estrutura de quadro ZR interna. A estrutura do quadro ZR é então adaptada ao mecanismo CFEC e ao DSP enquadrado para transmissão sobre a interface de mídia coerente.

Taxa de bits de aplicação | Taxa de Baud | Modulação | FEC |

478,75 Gb/s | 59.84375GBd | DP-16QAM | OFEC |

Anfitrião Conector Elétrico & Atribuições de Pin

As interfaces elétricas, incluindo atribuições de almofada para dados, controle, status e fontes de alimentação e requisitos de layout de PCB do host, do módulo é totalmente compatível com a QSFP-DD MSA QSFP-DD-Hardware Specification, rev 5.0.

O caso do módulo de QSFP-DD é isolado do aterramento do circuito do módulo, GND, para fornecer ao projetista do equipamento flexibilidade em relação às conexões entre escudos de interferência eletromagnética externos e aterramento do circuito, GND, do módulo.

Figura 2. Conector compatível com MSA

Pin # | Lógica | Símbolo | Deion | Sequência de plugue |

1 |

| GND | Chão | 1B |

2 | CML-I | Tx2n | Entrada de dados invertida do transmissor | 3B |

3 | CML-I | Tx2p | Entrada de dados não invertida do transmissor | 3B |

4 |

| GND | Chão | 1B |

5 | CML-I | Tx4n | Entrada de dados invertida do transmissor | 3B |

6 | CML-I | Tx4p | Entrada de dados não invertida do transmissor | 3B |

7 |

| GND | Chão | 1B |

8 | LVTTL-I | ModSelL | Módulo Selecionar | 3B |

9 | LVTTL-I | ResetL | Módulo Reset | 3B |

10 |

| VccRx | 3.3V Receptor da fonte de alimentação | 2B |

11 | LVCMOS-I/O | SCL | Relógio de interface serial de 2 fios | 3B |

12 | LVCMOS-I/O | SDA | Dados de interface serial de 2 fios | 3B |

13 |

| GND | Chão | 1B |

14 | CML-O | Rx3p | Saída de dados não invertida do receptor | 3B |

15 | CML-O | Rx3n | Saída de dados invertida do receptor | 3B |

16 | GND | Chão | 1B |

|

17 | CML-O | Rx1p | Saída de dados não invertida do receptor | 3B |

18 | CML-O | Rx1n | Saída de dados invertida do receptor | 3B |

19 |

| GND | Chão | 1B |

20 |

| GND | Chão | 1B |

21 | CML-O | Rx2n | Saída de dados invertida do receptor | 3B |

22 | CML-O | Rx2p | Saída de dados não invertida do receptor | 3B |

23 |

| GND | Chão | 1B |

24 | CML-O | Rx4n | Saída de dados invertida do receptor | 3B |

25 | CML-O | Rx4p | Saída de dados não invertida do receptor | 3B |

26 |

| GND | Chão | 1B |

27 | LVTTL-O | ModPrsL | Módulo Presente | 3B |

28 | LVTTL-O | IntL | Interromper | 3B |

29 |

| VccTx | Transmissor de fonte de alimentação 3.3V | 2B |

30 |

| Vcc1 | 3.3V Fonte de alimentação | 2B |

31 | LVTTL-I | InitMode | Modo de inicialização; Em aplicativos QSFP legados, o teclado InitMode é chamado de LPMODE | 3B |

32 |

| GND | Chão | 1B |

33 | CML-I | Tx3p | Entrada de dados não invertida do transmissor | 3B |

34 | CML-I | Tx3n | Entrada de dados invertida do transmissor | 3B |

35 |

| GND | Chão | 1B |

36 | CML-I | Tx1p | Entrada de dados não invertida do transmissor | 3B |

37 | CML-I | Tx1n | Entrada de dados invertida do transmissor | 3B |

38 |

| GND | Chão | 1B |

39 |

| GND | Chão | 1A |

40 | CML-I | Tx6n | Entrada de dados invertida do transmissor | 3A |

41 | CML-I | Tx6p | Entrada de dados não invertida do transmissor | 3A |

42 |

| GND | Chão | 1A |

43 | CML-I | Tx8n | Entrada de dados invertida do transmissor | 3A |

44 | CML-I | Tx8p | Entrada de dados não invertida do transmissor | 3A |

45 |

| GND | Chão | 1A |

46 |

| Reservado | Para uso futuro | 3A |

47 |

| VS1 | Módulo fornecedor específico 1 | 3A |

48 |

| VccRx1 | Fonte de alimentação 3.3V | 2A |

49 |

| VS2 | Módulo fornecedor específico 2 | 3A |

50 |

| VS3 | Módulo fornecedor específico 3 | 3A |

51 |

| GND | Chão | 1A |

52 | CML-O | Rx7p | Saída de dados não invertida do receptor | 3A |

53 | CML-O | Rx7n | Saída de dados invertida do receptor | 3A |

54 |

| GND | Chão | 1A |

55 | CML-O | Rx5p | Saída de dados não invertida do receptor | 3A |

56 | CML-O | Rx5n | Saída de dados invertida do receptor | 3A |

57 |

| GND | Chão | 1A |

58 |

| GND | Chão | 1A |

59 | CML-O | Rx6n | Saída de dados invertida do receptor | 3A |

60 | CML-O | Rx6p | Saída de dados não invertida do receptor | 3A |

61 |

| GND | Chão | 1A |

62 | CML-O | Rx8n | Saída de dados invertida do receptor | 3A |

63 | CML-O | Rx8p | Saída de dados não invertida do receptor | 3A |

64 |

| GND | Chão | 1A |

65 |

| NC | Sem conexão | 3A |

66 |

| Reservado | Para uso futuro | 3A |

67 |

| VccTx1 | Fonte de alimentação 3.3V | 2A |

68 |

| Vcc2 | Fonte de alimentação 3.3V | 2A |

69 |

| Reservado | Para o uso futuro | 3A |

70 |

| GND | Chão | 1A |

71 | CML-I | Tx7p | Entrada de dados não invertida do transmissor | 3A |

72 | CML-I | Tx7n | Entrada de dados invertida do transmissor | 3A |

73 |

| GND | Chão | 1A |

74 | CML-I | Tx5p | Entrada de dados não invertida do transmissor | 3A |

75 | CML-I | Tx5n | Entrada de dados invertida do transmissor | 3A |

76 |

| GND | Chão | 1A |

Avaliações máximas absolutas

Deve-se notar que a operação além de quaisquer classificações máximas absolutas individuais pode causar danos permanentes a este módulo.

Parâmetro | Min | Max | Unidades | Notas |

Temperatura de armazenamento | -40 | 85 | Ct |

|

Umidade de armazenamento (relativa) | - | 85 | % | Não-Condensação |

Caso temperatura | 0 | 75 | Ct |

|

Humidade de funcionamento (relativa) | - | 85 | % | Não-Condensação |

Temperatura do caso de operação de curto prazo |

| 80 | Ct | <24 horas |

Fonte de Alimentação Faixa Absoluta | -0,3 | 3.63 | V |

|

Potência de entrada máxima óptica RX | - | 10 | DBm |

|

Condições operacionais

Parâmetro | Min | Max | Unidades | Notas |

Temperatura do caso de funcionamento | 0 | 75 | Ct |

|

Humidade de funcionamento (relativa) | - | 85 | % | Não-Condensação |

Faixa de operação da fonte de alimentação | 3.135 | 3.465 | V |

|

Potência de entrada óptica RX | - | 0 | DBm |

|

Fonte de alimentação

O 400G ZR QSFP-DD DCO é um módulo Power Class 8. A fim de evitar exceder a capacidade de energia do sistema host, após o hot-plug, ciclo de energia ou reinicialização, todos os módulos de QSFP-DD devem ligar no modo de baixa potência se LPMode for afirmado. Se o LPMode não for afirmado, o módulo prosseguirá para o modo de alta potência sem intervenção do host. Os valores de especificação para correntes máximas instantâneas, sustentadas e de estado estacionário em cada classe de potência são indicados na tabela 5. Os requisitos de fonte de alimentação são especificados na tabela abaixo.

Parâmetro | Min | Típico | Max | Unidades | Notas |

3.3V DC Potência Tensão de alimentação | 3.135 | 3.3 | 3.465 | V |

|

3.3V DC Potência Atual de fornecimento |

|

| 7 | Um |

|

Dissipação de energia |

|

| 18 | W |

|

Baixo consumo de energia |

|

| 1.5 | W |

|

Módulo Inrush atual |

|

| 100 | MA/us |

|

Desligamento Atual

| -100 |

|

| MA/us |

|

Ruído da fonte de alimentação |

|

| 25 | MV |

|

Controle de hardware e pinos de status

Além da interface serial de 2 fios, o módulo possui os seguintes sinais de baixa velocidade para controle e status:

● ModSelL

● ResetL

● LPMode

● ModPrsL

● IntL

● Epps

ModSelL

O ModSelL é um sinal de entrada que deve ser puxado para Vcc no módulo QSFP-DD. Quando mantido baixo pelo host, o módulo responde a comandos de comunicação serial de 2 fios. O ModSelL permite o uso de vários módulos de QSFP-DD em um único barramento de interface de 2 fios. Quando ModSelL é “Alto”, o módulo não deve responder ou reconhecer qualquer comunicação de interface de 2 fios do host.

A fim de evitar conflitos, o sistema host não deve tentar comunicações de interface de 2 fios dentro do tempo de desafirmação ModSelL após a escritura de quaisquer módulos de QSFP-DD. Da mesma forma, o host deve esperar pelo menos pelo período do tempo de afirmação ModSelL antes de se comunicar com o módulo recém-criado. Os períodos de afirmação e desafirmação de diferentes módulos podem se sobrepor desde que os requisitos de tempo acima sejam atendidos.

ResetL

O sinal ResetL deve ser puxado para Vcc no módulo. Um nível baixo no sinal ResetL por mais tempo do que o comprimento de pulso mínimo (t_Reset_init) inicia uma redefinição completa do módulo, retornando todas as configurações do módulo do usuário ao seu estado padrão.

LPMode

LPMode é um sinal de entrada. O sinal LPMode deve ser puxado até Vcc no módulo QSFP-DD. LPMode é usado no controle do modo de energia do módulo.

Ver secção 6.3.1.3 do CMIS.

ModPrsL

ModPrsL deve ser puxado para cima para Vcc Host na placa de host e puxado para baixo no módulo. O ModPrsL é declarado “Baixo” quando o módulo é ed. O ModPrsL é desafirmado “Alto” quando o módulo está fisicamente ausente do conector host devido ao resistor pull-up na placa host.

A sinalização de baixa velocidade, exceto a interface SCL e SDA, é baseada no TTL de baixa tensão (LVTTL) operando em Vcc. Vcc refere-se às tensões de fornecimento genéricas de VccTx, VccRx, Vcc host ou Vcc1. Os hosts devem usar um resistor de pull-up conectado ao host Vcc em cada um dos SCL de interface de 2 fios (relógio), SDA (dados) e todas as saídas de status de baixa velocidade. O SCL e SDA é uma interface hot plug que pode suportar uma topologia de barramento. Durante o íon ou remoção do módulo, o módulo pode implementar um circuito pré-ge que evita a corrupção de transferências de dados de outros módulos que já estão usando o barramento.

As especificações elétricas de baixa velocidade QSFP-DD são fornecidas na tabela 6. Esta especificação garante a compatibilidade entre os barramentos de host e a interface de 2 fios.

Parâmetro | Símbolo | Min | Max | Unidade | Condição |

SCL e SDA | VOL | 0 | 0,4 | V | IOL(max)= 3 mA para o modo rápido, 20 mA para Fast-mode plus |

SCL e SDA | VIL | -0,3 | Vcc * 0,3 | V |

|

VIH | Vcc * 0,7 | Vcc 0,5 | V |

|

Capacitância para SCL e SDA Sinal de I/O | Ci |

| 14 | PF |

|

Total de ônibus Carga capacitiva Para SCL e SDA | Cb |

| 100 | PF | Para taxa de clock de 400 kHz, use resistor de pull-up de 3,0 k Ohms, máx. |

|

| 200 | PF | Para taxa de clock de 400 kHz, use o resistor Pull-up de 1,6 k Ohms, máx. |

LPMode, ResetL, ModSelL E EPPS | VIL | -0,3 | 0,8 | V |

|

VIH | 2 | Vcc 0,3 | V |

|

LPMode, ResetL E ModSelL | | Iin | |

| 360 | UA | 0V |

EPPS | | Iin | |

| TBD | UA | 0V |

IntL | VOL | 0 | 0,4 | V | IOL = 2.0 mA |

VOH | Vcc-0,5 | Vcc 0,3 | V | 10k Ohms pull-up para Host Vcc |

ModPrsL | VOL | 0 | 0,4 | V | IOL = 2.0 mA |

VOH |

|

| V | ModPrsL pode ser implementado como um curto-circuito para GND no módulo |

Camada Física

A camada física que suporta a comunicação entre o host e o módulo é a Interface serial de dois fios (TWI). O TWI consiste em um sinal de relógio (SCL) e um sinal de dados (SDA).

SCL e SDA compreendem uma interface serial de 2 fios entre o host e o módulo usando o protocolo TWI. SCL é definido como o sinal de clock da interface serial e SDA como o sinal de dados da interface serial. Ambos os sinais são abertos e requerem resistores pull-up para 3,3 V no host. O valor do resistor pull-up deve ser de 1k ohms a 4,7 k ohms, dependendo da carga capacitiva.

Ambos os sinais (SCL e SDA) são pinos bidirecionais de coletor aberto e requerem um pull-up externo para VCC no PCB host. Ativar a linha requer puxá-la para baixo (com fio). A capacitância total no ônibus não deve exceder 400pF.

Esta interface de 2 fios suporta velocidades de barramento:

· Modo rápido-Modo rápido I2C (Fm) ≤ 400 kbit/s

· Modo rápido mais-modo rápido I2C Plus (Fm +) ≤ 1 Mbit/s

O sinal SDA é bidirecional. Durante a transferência de dados binários, o sinal SDA fará a transição quando o SCL estiver baixo. As transições SDA quando SCL é alto são usadas para marcar o início (START) ou o término (STOP) de uma transferência de dados.

Especificações elétricas de alta velocidade

O transmissor e o receptor estão em conformidade com a especificação elétrica CEI-56G-VSR-PAM4 (OIF-CEI-04.0).

As linhas de dados são acopladas a CA e terminadas no módulo de acordo com a figura a seguir do QSFP-DD MSA. Os sinais de alta velocidade seguem as especificações elétricas dos CEI-56G-VSR-PAM, conforme definido na OIF-CEI-04.0.

Os sinais de alta velocidade consistem em 8 pares diferenciais de transmissão e 8 receptores identificados como TX[8:1]p / TX[8:1]n e RX[8:1]p / RX[8:1]n. Esses sinais podem ser operados em 400GAUI-8 dependendo da capacidade do modo host.400GAUI-8 fornece 8 faixas diferenciais usando sinalização PAM4 operando a 26,5625 GBaud. Isso resulta em 8 faixas de 50 Gb/s para um total de 400 Gb/s. Este modo permite a conexão com configurações PMD de 400GUAI-8.

As seguintes acterísticas elétricas são definidas no ambiente operacional recomendado, a menos que especificado de outra forma.

Características elétricas para o transmissor

Parâmetro | Min | Típico | Max | Unidades | Notas |

Taxa de sinal, Cada pista | 26,5625 ± 100ppm | GBaud |

|

Diferencial Entrada de pico-pico Tolerância de tensão |

|

| 900 | MVpp |

|

Características elétricas para o receptor

Parâmetro | Min | Típico | Max | Unidades | Notas |

Taxa de sinal, Cada pista | 26,5625 ± 100ppm | GBaud |

|

Diferencial Entrada de pico-pico Tolerância de tensão |

| 750 | 900 | MVpp |

|

Tempo de Transição, 20% a 80% |

| 9,5 |

| Ps |

|

Loopback

A funcionalidade de loopback do suporte do módulo. O loopback do host (Loopback imbardo) e o loopback da rede (Loopback sebing) são mostrados na figura 4. Para obter detalhes sobre como controlar o modo de loopback, consulte a Referência [2]. Em loopback opcional, o TXn é reconectado ao RXn, por exemplo, TX0 a RX0, tanto no host quanto no lado da mídia.

Figura 3: Módulo de Orientação de Loopback

Especificações ópticas

Todas as especificações fornecidas neste documento são números de fim de vida útil e são válidas sob condições operacionais, a menos que especificado:

Especificações do transmissor óptico

Parâmetro | Min | Typ. | Max | Unidade | Notas |

Transmissor Frequência Alcance | 191.3 | 193.7 | 196.1 | THz | Banda C grade ITU-T de 75GHz. Faixa de frequência sobre a qual as especificações se mantêm, a menos que indicado de outra forma. |

Estabilidade de frequência do laser | -1,8 |

| 1.8 | GHz | Estabilidade de frequência em relação à grade ITU. |

Laser Frequência Precisão | -1,8 |

| 1.8 | GHz |

|

Frequência do laser Faixa de ajuste fino | -6.0 |

| 6.0 | GHz |

|

Resolução de ajuste fino |

| 100 |

| MHz |

|

Velocidade de ajuste do canal | - |

| 60 | S |

|

Largura da linha do laser |

|

| 100 | KHz |

|

Saída do transmissor Faixa de potência |

| -9,5 |

| DBm |

|

Transmissor Laser Desativar o tempo |

|

| 180 | Ms |

|

Estabilidade potência de saída | -0,5 |

| 0,5 | DB | Diferença sobre temperatura, tempo, comprimento de onda e envelhecimento. |

Precisão potência de saída | -2 |

| 2 | DB | Diferença entre o valor definido e Valor real sobre o envelhecimento. |

Transmissor Tempo de Turn-up Do começo frio | - |

| 120 | S |

|

Transmissor OSNR (Inband) | 34 |

| - | DB/0.1nm |

|

Transmissor Reflectância traseira | - |

| -24 | DB |

|

Potência de saída do transmissor Com TX Desativado | - |

| -20 | DBm |

|

Transmissor Polarização Poder dependente | - |

| 1.5 | DB | Deferência de poder entre a polarização X e Y |

Especificações do receptor óptico

Parâmetro | Min | Typ. | Max | Unidade | Notas |

Faixa de frequência do receptor | 191.3 | 193.7 | 196.1 | THz |

|

Faixa de potência de entrada | -12 |

| 0 | DBm | Potência de sinal do canal na penalidade OSNR <0.5dB |

Sensibilidade OSNR |

| 24 | 26 | DB/0.1nm |

|

Sensibilidade do receptor |

|

| -20 | DBm | Potência de entrada necessária para alcançar pós FEC BER < 1E-15 quando OSNR Tolerância> 26dB/0.1nm |

Los Assert | -24 |

| -20 | DBm |

|

Los Histerese | 1.0 |

| 2.5 | DB |

|

Tolerância CD | 2400 |

|

| Ps/nm | Tolerância à dispersão cromática. |

Tolerância PMD | 10 |

|

| Ps | Tolerância a PMD com <0,5 dB de penalidade para sensibilidade OSNR. |

Tolerância PDL de pico | 3.5 |

|

| DB | Tolerância ao pico PDL com <1,3 dB de penalidade para sensibilidade OSNR quando a mudança no SOP é <= 1 rad/ms. |

Tolerância a Mudança no SOP | 50 |

| - | Rad/ms |

|

Potência de entrada Tolerância transitória | -2 |

| 2 | DB | Tolerância para alterar a potência de entrada com <0,5 dB de penalidade para sensibilidade OSNR. |

Potência de entrada Precisão de leitura | -2 |

| 2 | DB |

|

Perda de retorno óptico | -20 |

|

| DB | Reflectância óptica na entrada do conector Rx. |

Receptor Turn-up Tempo Do começo frio | - |

| 120 | S | A partir do reset do módulo, com sinal de entrada óptica válido presente. |

Força de inserção, extração e retenção

Parâmetro | Min | Max | Unidade | Nota |

Força de inserção |

| 90 | N |

|

Força de extração |

| 50 | N |

|

Força de retenção | 90 |

| N |

|

Especificação EMI, EMC e ESD

O módulo está em conformidade com os requisitos listados na tabela abaixo quando instalado no equipamento host.

Parâmetro | Referência | Valor | Unidade | Notas |

Imunidade ESD | IEC 61000-4-2 | 8 | KV | Contate Disge |

15 | KV | Disge do ar |

ESD (modelo HBM) | JESD22-A114-B JEDEC | 1 | KV | Contatos de alta velocidade |

2 | KV | Outros pinos |

Imunidade EMC | IEC 61000-4-3 |

|

|

|

Emissão EMI | FCC Classe B |

|

|

|

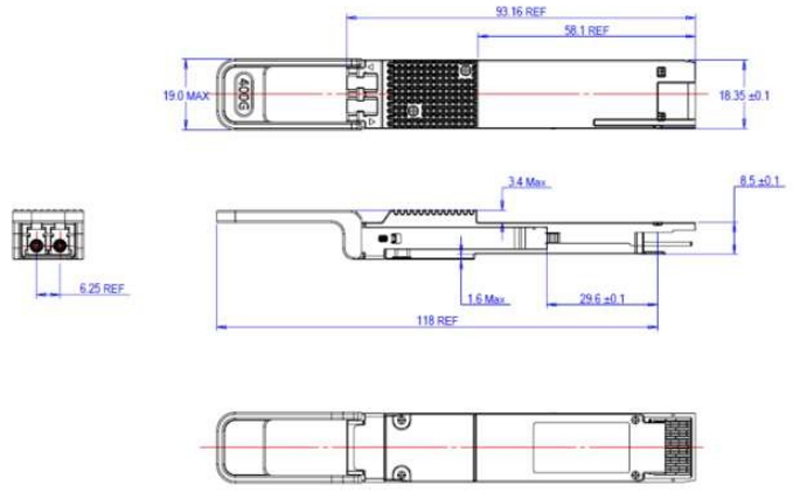

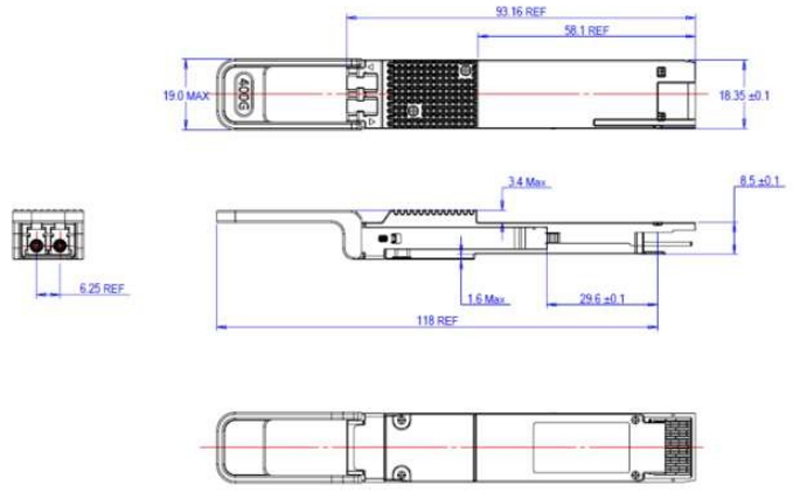

Desenho de contorno (mm)

Figura 4: Módulo QSFP-DD Desenho mecânico

Centro de dados da Internet

Centro de dados da Internet Perguntas frequentes

Perguntas frequentes Notícias da Indústria

Notícias da Indústria Sobre nós

Sobre nós Interruptor do centro de dados

Interruptor do centro de dados  Interruptor da empresa

Interruptor da empresa  Interruptor industrial

Interruptor industrial  Interruptor de acesso

Interruptor de acesso  Rede integrada

Rede integrada  Módulo óptico & Cabo

Módulo óptico & Cabo

Ligue para nós:

Ligue para nós:  Envie-nos um e-mail:

Envie-nos um e-mail:  2106B, # 3D, Cloud Park Fase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Fase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.